# Motorola MVME147-012

25MHz, 8MB Single Board Computer

Limited Availability

Used and in Excellent Condition

**Buy Today!**

https://www.artisantg.com/59098-14

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

Your **definitive** source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

# **Description of 147Bug**

The MVME147Bug package is a powerful evaluation and debugging tool for systems built around the MVME147 monoboard microcomputer. Facilities are available for loading and executing user programs under complete operator control for system evaluation. The 147Bug includes commands for display and modification of memory, breakpoint capabilities, a powerful assembler/disassembler useful for patching programs, and a self test power up feature which verifies the integrity of the system. Various 147Bug routines that handle I/O, data conversion, and string functions are available to user programs through the TRAP #15 handler.

Caution

When using the 147Bug TRAP #15 functions, the interrupt mask is raised to level 7 and the MMU is disabled during the TRAP #15 function.

In addition, 147Bug provides as an option a "system" mode that allows autoboot on power up or reset, and a menu interface to several system commands used in VME Delta Series systems.

The 147Bug consists of three parts: a command-driven user-interactive software debugger, described in Chapter 2 and hereafter referred to as the debugger, a command-driven diagnostic package for the MVME147 hardware, described in Chapter 6 and hereafter referred to as the diagnostics, and a user interface which accepts commands from the system console terminal.

When using 147Bug, you operate out of either the debugger directory or the diagnostic directory. If you are in the debugger directory, then the debugger prompt "147-Bug>" is displayed and you have all the debugger commands at your disposal. If in the diagnostic directory, then the diagnostic prompt "147-Diag>" is displayed and you have all the diagnostic commands at your disposal as well as all of the debugger commands. You may switch between directories by using the Switch Directories (**SD**) command or may examine the commands in the particular directory that you are currently in by using the Help (**HE**) command (refer to Chapter 3).

# Note

If you have the MVME147SRF MPU module all references to Ethernet should be disregarded. If you are in the debugger directory, then the debugger prompt "147RF-Bug>" is displayed and you have all the debugger commands at your disposal. If in the diagnostic directory, then the diagnostic prompt "147RF-Diag>" is displayed and you have all the diagnostic commands at your disposal as well as all of the debugger commands.

Because 147Bug is command-driven, it performs its various operations in response to your commands entered at the keyboard. The flow of control in normal 147Bug operation is illustrated in Figure 1-1. The flow of control in system 147Bug operation is illustrated in Figure 1-2. When a command is entered, 147Bug executes the command and the prompt reappears. However, if a command is entered which causes execution of your target code (for example, **GO**), then control may or may not return to 147Bug, depending on the outcome of the program.

The commands are more flexible and powerful than previous debuggers. Also, the debugger in general is more "user-friendly", with more detailed error messages (refer to Appendix B) and an expanded online help facility.

#### Figure 1-1. Flow Diagram of 147Bug (Normal) Operational Mode

Figure 1-2. Flow Diagram of 147Bug (System) Operational Mode

## **How to Use This Manual**

If you have never used a debugging package before you should read all of Chapter 1 before attempting to use 147Bug. This gives an idea of 147Bug structure and capabilities.

The *Installation and Startup* section describes a step-by-step procedure to power up the module and obtain the 147Bug prompt on the terminal screen.

For a question about syntax or operation of a particular 147Bug command, you may turn to the entry for that particular command in the chapter describing the command set (refer to Chapter 3).

Some debugger commands take advantage of the built-in one-line assembler/disassembler. The command descriptions in Chapter 3 assume that you already understand how the assembler/disassembler works. Refer to the assembler/disassembler description in Chapter 4 for details on its use.

# Note

In the examples shown, all your input is in BOLD. This is done for clarity in understanding the examples (to distinguish between characters input by you and characters output by 147Bug). The symbol (CR) represents the carriage return key on the terminal keyboard. Whenever this symbol appears, it means a carriage return entered by the user.

## **Installation and Startup**

Even though the MVME147Bug EPROMs are installed on the MVME147 module, for 147Bug to operate properly with the MVME147, follow this set-up procedure. Refer to the MVME147/MVME147S MPU VMEmodule User's Manual for header and parts locations.

# Caution

Inserting or removing modules while power is applied could damage module components.

1. Turn all equipment power OFF. Configure the header jumpers on the module as required for your particular application.

For the MVME147, MVME147A, MVME147-1, and MVME147A-1 the only jumper configurations specifically dictated by 147Bug are those on header J3. Header J3 must be configured with jumpers positioned between pins 2-4, 3-5, 6-8, 13-15, and 14-16. This sets EPROM sockets U1 and U2 for 128K x 8 devices. This is the factory configuration for these modules.

For the MVME147S, MVME147SA, MVME147S-1, MVME147SA-1, MVME147SA-2, MVME147SB-1, MVME147SC-1, and MVME147SRF the only jumper configurations specifically dictated by 147Bug are those on header J2. Header J2 must be configured with jumpers positioned between pins 2-4, 3-5, 6-8, 13-15, and 14-16. This sets EPROM sockets U22 and U30 for 128K x 8 devices. This is the factory configuration for these modules.

2. For the MVME147, MVME147A, MVME147-1, and MVME147A-1 configure header J5 for your particular application. Header J5 enables or disables the system controller function.

For the MVME147S, MVME147SA, MVME147S-1, MVME147SA-1, MVME147SA-2, MVME147SB-1, MVME147SC-1, and MVME147SRF configure header J3 for your particular application. Header J3 enables or disables the system controller function.

# Caution

Be sure chip orientation is correct, with pin 1 oriented with pin 1 silkscreen markings on the board.

3. For the MVME147, MVME147A, MVME147-1, and MVME147A-1 be sure that the two 128K x 8 147Bug EPROMs are installed in sockets U1 (even bytes, even BXX label) and U2 (odd bytes, odd BXX label) on the MVME147 module.

For the MVME147S, MVME147SA, MVME147S-1, MVME147SA-1, MVME147SA-2, MVME147SB-1, MVME147SC-1, and MVME147SRF be sure that the two 128K x 8 147Bug EPROMs are installed in sockets U22 (even bytes, even BXX label) and U30 (odd bytes, odd BXX label) on the MVME147 module.

- 4. Refer to the set-up procedure for the your particular chassis or system for details concerning the installation of the MVME147.

- 5. Connect the terminal which is to be used as the 147Bug system console to connector J7 (port 1) on the MVME712/MVME712M front panel. Set up the terminal as follows:

- eight bits per character

- one stop bit per character

- parity disabled (no parity)

- 9600 baud to agree with default baud rate of the MVME147 ports at power-up.

After power up, the baud rate of the J7 port (port 1) can be reconfigured by using the Port Format (**PF**) command of the 147Bug debugger.

# Note

In order for high-baud rate serial communication between 147Bug and the terminal to work, the terminal must do some handshaking. If the terminal being used does not do hardware handshaking via the CTS line, then it must do

XON/XOFF handshaking. If you get garbled messages and missing characters, then you should check the terminal to make sure XON/XOFF handshaking is enabled.

- 6. If you want to connect device(s) (such as a host computer system or a serial printer) to ports 2, 3, and/or port 4 on the MVME712/MVME712M, connect the appropriate cables and configure the port(s) as detailed in the MVME147/MVME147S MPU VMEmodule User's Manual. After power up, these ports can be reconfigured by using the **PF** command of the 147Bug debugger.

- 7. Power up the system. The 147Bug executes self-checks and displays the debugger prompt "147-Bug>".

If after a delay, the 147Bug begins to display test result messages on the bottom line of the screen in rapid succession, the MVME147 is in the 147Bug "system" mode. If this is not the desired mode of operation, then press the ABORT switch on the front panel of the MVME147. When the MENU is displayed, enter a 3 to go to the system debugger. The environment may be changed by using the Set Environment (ENV) command. Refer to the Bug operation in the system mode in this manual.

When power is applied to the MVME147, bit 1 at location \$FFFE1029 (Peripheral Channel Controller (PCC) general purpose status register) is set to 1 indicating that power was just applied. (Refer to MVME147/MVME147S MPU VMEmodule User's Manual for a description of the PCC.) This bit is tested within the "Reset" logic path to see if the power up confidence test needs to be executed. This bit is cleared by writing a 1 to it thus preventing any future power up confidence test execution.

If the power up confidence test is successful and no failures are detected, the firmware monitor comes up normally, with the FAIL LED off.

If the confidence test fails, the test is aborted when the first fault is encountered and the FAIL LED remains on. If possible, one of the following messages is displayed:

```

... 'CPU Register test failed'

... 'CPU Instruction test failed'

... 'ROM test failed'

... 'RAM test failed'

... 'CPU Addressing Modes test failed'

... 'Exception Processing test failed'

... '+12v fuse is open'

```

```

... 'Battery low (data may be corrupted)'

... 'Unable to access non-volatile RAM properly'

```

The firmware monitor comes up with the FAIL LED on.

### **Autoboot**

Autoboot is a software routine that can be enabled by a flag in the battery backed-up RAM to provide an independent mechanism for booting an operating system. When enabled by the Autoboot (AB) command, this autoboot routine automatically starts a boot from the controller and device specified. It also passes on the specified default string. This normally occurs at power-up only, but you may change it to boot up at any board reset. NOAB disables the routine but does not change the specified parameters. The autoboot enable/disable command details are described in Chapter 3. The default (factory-delivered) condition is with autoboot disabled.

If, at power up, Autoboot is enabled and the drive and controller numbers provided are valid, the following message is displayed on the system console:

```

"Autoboot in progress... To Abort hit <BREAK>"

```

Following this message there is a delay while the debug firmware waits for the various controllers and drives to come up to speed. Then the actual I/O is begun: the program pointed to within the volume ID of the media specified is loaded into RAM and control passed to it. If, however, during this time, you want to gain control without Autoboot, hit the <BREAK> key.

## Caution

This information applies to the MVME350 module but not the MVME147. Although streaming tape can be used to autoboot, the same power supply must be connected to the streaming tape drive, controller, and the MVME147. At power up, the tape controller positions the streaming tape to load point where the volume ID can correctly be read and used.

If, however, the MVME147 loses power but the controller does not, and the tape happens not to be at load point, the sequences of commands required (attach and rewind) cannot be given to the controller and autoboot is not successful.

## **ROMboot**

This function is enabled by the ROMboot (**RB**) command and executed at power up (optionally also at reset), assuming there is valid code in the ROMs (or optionally elsewhere on the module or VMEbus) to support it. If ROMboot code is installed and the environment has been set for Bug mode (refer to the *Set Environment to Bug/Operating System (ENV)* section in Chapter 3), a userwritten routine is given control (if the routine meets the format requirements). One use of ROMboot might be resetting SYSFAIL\* on an unintelligent controller module. The **NORB** command disables the function. For your module to gain control through the ROMboot linkage, four requirements must be met:

- 1. Power must have just been applied (but the **RB** command can change this to also respond to any reset).

- 2. Your routine must be located within the MVME147 ROM memory map (but the RB command can change this to any other portion of the onboard memory, or even offboard VMEbus memory).

- 3. The ASCII string "BOOT" must be located within the specified memory range.

- 4. Your routine must pass a checksum test, which ensures that this routine was really intended to receive control at power up.

To prepare a module for ROMboot, the Checksum (**CS**) command must be used. When the module is ready it can be loaded into RAM, and the checksum generated, installed, and verified with the **CS** command. (Refer to the **CS** command description and examples.)

The format of the beginning of the routine is as follows:

| MODULE |         |                |                                                                       |

|--------|---------|----------------|-----------------------------------------------------------------------|

| OFFSET | LENGTH  | CONTENTS       | DESCRIPTION                                                           |

| \$00   | 4 bytes | BOOT           | ASCII string indicating possible routine; checksum must be zero, too. |

| \$04   | 4 bytes | Entry Address  | Longword offset from "BOOT".                                          |

| \$08   | 4 bytes | Routine Length | Longword, includes length from "BOOT" to and including checksum.      |

| \$0C   | ?       | Routine name   | ASCII string containing routine name.                                 |

By convention within Motorola, the last three bytes of ROM contain the firmware version number, checksum, and socket number. In this environment, the length would contain the ASCII string "BOOT", through and including the socket number; however, if you wish to make use of ROMboot you do not have to fill a complete ROM. Any partial amount is acceptable, as long as the length reflects where the checksum is correct.

ROMboot searches for possible routines starting at the start of the memory map first and checks for the "BOOT" indicator. Two events are of interest for any location being tested:

- 1. The map is searched for the ASCII string "BOOT".

- 2. If the ASCII string "BOOT" is found, it is still undetermined whether the routine is meant to gain control at power up or reset. To verify that this is the case, the bytes starting from 'BOOT' through the end of the routine (as defined by the 4-byte length at offset \$8) are run through the self-test checksum routine. If both the even and odd bytes are zero, it is established that the routine was meant to be used for ROMboot.

Under control of the **RB** command, the sequence of searches is as follows:

- Search direct address for "BOOT".

- 2. Search your non-volatile RAM (first 1K bytes of battery back-up RAM).

- 3. Search complete ROM map.

- 4. Search local RAM (if **RB** command has selected to operate on any reset), at all 8K byte boundaries starting at \$00004000.

- 5. Search the VMEbus map (if so selected by the **RB** command) on all 8K byte boundaries starting at the end of the onboard RAM.

The following example performs the following:

- 1. Outputs a (CR)(LF) sequence to the default output port.

- 2. Displays the date and time from the current cursor position.

- 3. Outputs two more (CR)(LF) sequences to the default output port.

- Returns control to 147Bug.

# Note

This example assumes that the target code is temporarily loaded into the MVME147 RAM. However, an emulator such as the Motorola HDS-300 or HDS-400 could easily be used to load and modify the target code in its actual execution location.

$SAMPLE\ ROMboot\ ROUTINE\ -\ Module\ preparation\ including\ calculation\ of\ checksum.$

The target code is first assembled and linked, leaving \$00 in the even and odd locations destined to contain the checksum.

Load the routine into RAM (with S-records via the **LO** command, or from a disk using **IOP**).

# 147-Bug>**mds 6000**Display entire module (zero checksums at \$0000602C and \$0000602D).

| 00006000<br>BOOT      |      |       | 0000 | 0018 | 0000 | 002E | 5465 | 7374 |

|-----------------------|------|-------|------|------|------|------|------|------|

| 00006010<br>ROMbootNO | 2052 | 4F4D  | 424F | 4F54 | 4E4F | 0026 | 4E4F | 0052 |

| 00006020<br>NO.&NO.&N |      |       | 4E4F | 0026 | 4E4F | 0063 | 0000 | 0000 |

| 00006030              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 00006040              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 00006050              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 00006060              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 00006070              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 00006080              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 00006090              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 000060A0              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 000060B0              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 000060C0              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 000060D0              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| 000060E0              | 0000 | 0000  | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |

| • • • • • • • •       |      | • • • |      |      |      |      |      |      |

1-9

#### 147-Bug>md 6018;diDisassemble executable instructions.

```

00006018 4E4F0026SYSCALL.PCRLF

0000601C 4E4F0052SYSCALL.RTC_DSP

00006020 4E4F0026SYSCALL.PCRLF

00006024 4E4F0026SYSCALL.PCRLF

00006028 4E4F0063SYSCALL.RETURN

0000602C 00000000ORI.B#$0,D0

00006030 0000000ORI.B #$0,D0

00006034 0000000ORI.B #$0,D0

```

#### 147-Bug>CS 6000 602EPerform checksum on locations 6000

Physical Address=00006000 0000602Dthrough 602E (refer to CS command).

(Even Odd)=F99F

#### 147-Bug> **M 602C**;**B**Insert checksum into bytes \$602C,\$602D.

0000602C 00 ?F9 0000602D 00 ?9F.

#### 147-Bug>**CS 6000 602E**

Physical Address=00006000 0000602DVerify that the checksum is correct. (Even Odd)=0000

# 147-Bug> **mds 6000**Again display entire module (now with checksums).

```

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

00006000 0000 0000 0000 0000 0000 0000 0000

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

147-Bug>

```

The routine is now recognized by the ROMboot function when it is enabled by the **RB** command.

## Restarting the System

You can initialize the system to a known state in three different ways. Each has characteristics which make it more appropriate than the others in certain situations.

#### Reset

Pressing and releasing the MVME147 front panel RESET switch initiates a system reset. COLD and WARM reset modes are available. By default, 147Bug is in COLD mode (refer to the RESET command description). During COLD reset, a total system initialization takes place, as if the MVME147 had just been powered up. The breakpoint table and offset registers are cleared. The target registers are invalidated. Input and output character queues are cleared. Onboard devices (timer, serial ports, etc.) are reset. All static variables (including disk device and controller parameters) are restored to their default states. Serial ports are reconfigured to their default state.

During WARM reset, the 147Bug variables and tables are preserved, as well as the target state registers and breakpoints. If the particular MVME147 is the system controller, then a system reset is issued to the VMEbus and other modules in the system are reset as well.

The local reset feature (the MVME147 is NOT the system controller) is a partial system reset, not a complete system reset such as power up or SYSRESET. When the local bus reset signal is asserted, a local bus cycle may be aborted. Because the VMEchip is connected to both the local bus and the VMEbus, if the aborted cycle is bound for the VMEbus, erratic operation may result. Communications between the local processor and the VMEbus should be terminated by an abort, reset should be used only when the local processor is halted or the local bus is hung and reset is the last resort.

Reset must be used if the processor ever halts (as evidenced by the MVME147 illuminated STATUS LED), for example after a double bus fault; or if the 147Bug environment is ever lost (vector table is destroyed, etc.).

#### **Abort**

Abort is invoked by pressing and releasing the ABORT switch on the MVME147 front panel. Whenever abort is invoked when executing a user program (running target code), a "snapshot" of the processor state is captured and stored in the target registers. (When working in the debugger, abort captures and stores only the program counter, status register, and format/vector information.) For this reason, abort is most appropriate when terminating a user program that is being debugged. Abort should be used to regain control if the program gets caught in a loop, etc. The target PC, stack pointers, etc., help to pinpoint the malfunction.

Abort generates a level seven interrupt (non-maskable). The target registers, reflecting the machine state at the time the ABORT switch was pushed, are displayed to the screen. Any breakpoints installed in your code are removed and the breakpoint table remains intact. Control is returned to the debugger.

## Reset and Abort - Restore Battery Backed Up RAM

Pressing both the RESET and ABORT switches at the same time and releasing the RESET switch before the ABORT switch initiates an onboard reset and a restore of Key Bug dependent BBRAM variables.

During the start of the reset sequence, if abort is invoked, then the following conditions are set in BBRAM:

□ SCSI ID set to 7.

| Ш | Memory sized flag is cleared (onboard memory is sized on this reset). |

|---|-----------------------------------------------------------------------|

|   | AUTOboot (Bug "normal") is turned off.                                |

|   | ROMboot (Bug "normal") is turned off.                                 |

|   | Environment set for Bug "normal" mode.                                |

|   | Automatic SCSI bus reset is turned off.                               |

|   | Grafix board switch is turned off.                                    |

|   | Onboard diagnostic switch is turned on (for this reset only).         |

|   | System memory sizing is turned on (System mode).                      |

|   | Console set to port 1 (LUN 0).                                        |

|   | Port 1 (LUN 0) set to use ROM defaults for initialization.            |

|   | Concurrent mode is turned off.                                        |

In this situation, if a failure occurs during the onboard diagnostics, the FAIL LED repeatedly flashes a code to indicate the failure. The on/off LED time for code flashing is approximately 0.25 seconds. The delay between codes is approximately two seconds. To complete bug initialization, press the ABORT switch while the LED is flashing. When initialization is complete, a failure message is displayed. LED flashes indicate confidence test failures per the following table.

|    | Number of LED Flashes | Description                           |

|----|-----------------------|---------------------------------------|

| 1  |                       | CPU register test failure             |

| 2  |                       | CPU instruction test failure          |

| 3  |                       | ROM test failure                      |

| 4  |                       | Onboard RAM test (first 16KB) failure |

| 5  |                       | CPU addressing mode test failure      |

| 6  |                       | CPU exception processing test failure |

| 7  |                       | +12 Vdc fuse failure                  |

| 10 |                       | NVRAM battery low                     |

| 11 |                       | Trouble with the NVRAM                |

| 12 |                       | Trouble with the RTC                  |

#### **Break**

A "Break" is generated by pressing and releasing the BREAK key on the terminal keyboard. Break does not generate an interrupt. The only time break is recognized is when characters are sent or received by the console port. Break removes any breakpoints in your code and keeps the breakpoint table intact. Break does not, however, take a snapshot of the machine state nor does it display the target registers.

Many times it is desired to terminate a debugger command prior to its completion, for example, the display of a large block of memory. Break allows you to terminate the command without overwriting the contents of the target registers, as would be done if abort were used.

## **Memory Requirements**

The program portion of 147Bug is approximately 256Kb of code. The EPROM sockets on the MVME147 are mapped at locations \$FF800000 through \$FF83FFFF. However, 147Bug code is position-independent and executes anywhere in memory; SCSI firmware code is not position-independent.

The 147Bug requires a minimum of 16Kb of read/write memory to operate. This memory is the MVME147 onboard read/write memory, ensuring standalone operation of the MVME147. When programming the PCC slave base address register, in order to select the address at which onboard RAM appears from the VMEbus, refer to the table below.

|      |      |      |      |      | BEGINN<br>ING       | ENDING                  |       |

|------|------|------|------|------|---------------------|-------------------------|-------|

| RBA4 | RBA3 | RBA2 | RBA1 | RBA0 | ADDRES<br>S         | ADDRES<br>S             | NOTES |

| 0    | 0    | 0    | 0    | 0    | \$00000000          | (1 x<br>DRAMsiz<br>e)-1 |       |

| 0    | 0    | 0    | 0    | 1    | 1 x<br>DRAMsiz<br>e | (2 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 0    | 0    | 0    | 1    | 0    | 2 x<br>DRAMsiz<br>e | (3 x<br>DRAMsiz<br>e)-1 | 1,2   |

Table 1-1. DRAM Address as Viewed from the VMEbus

Table 1-1. DRAM Address as Viewed from the VMEbus

|      | ı    | ı    | T    | 1    | 1                    | 1                        |       |

|------|------|------|------|------|----------------------|--------------------------|-------|

|      |      |      |      |      | BEGINN<br>ING        | ENDING                   |       |

| RBA4 | RBA3 | RBA2 | RBA1 | RBA0 | ADDRES<br>S          | ADDRES<br>S              | NOTES |

| 0    | 0    | 0    | 1    | 1    | 3 x<br>DRAMsiz<br>e  | (4 x<br>DRAMsiz<br>e)-1  | 1,2   |

| 0    | 0    | 1    | 0    | 0    | 4 x<br>DRAMsiz<br>e  | (5 x<br>DRAMsiz<br>e)-1  | 1,2   |

| 0    | 0    | 1    | 0    | 1    | 5 x<br>DRAMsiz<br>e  | (6 x<br>DRAMsiz<br>e)-1  | 1,2   |

| 0    | 0    | 1    | 1    | 0    | 6 x<br>DRAMsiz<br>e  | (7 x<br>DRAMsiz<br>e)-1  | 1,2   |

| 0    | 0    | 1    | 1    | 1    | 7 x<br>DRAMsiz<br>e  | (8 x<br>DRAMsiz<br>e)-1  | 1,2   |

| 0    | 1    | 0    | 0    | 0    | 8 x<br>DRAMsiz<br>e  | (9 x<br>DRAMsiz<br>e)-1  | 1,2   |

| 0    | 1    | 0    | 0    | 1    | 9 x<br>DRAMsiz<br>e  | (10 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 0    | 1    | 0    | 1    | 0    | 10 x<br>DRAMsiz<br>e | (11 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 0    | 1    | 0    | 1    | 1    | 11 x<br>DRAMsiz<br>e | (12 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 0    | 1    | 1    | 0    | 0    | 12 x<br>DRAMsiz<br>e | (13 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 0    | 1    | 1    | 0    | 1    | 13 x<br>DRAMsiz<br>e | (14 x<br>DRAMsiz<br>e)-1 | 1,2   |

Table 1-1. DRAM Address as Viewed from the VMEbus

|      |      |      |      |      | BEGINN<br>ING        | ENDING                   |       |

|------|------|------|------|------|----------------------|--------------------------|-------|

| RBA4 | RBA3 | RBA2 | RBA1 | RBA0 | ADDRES<br>S          | ADDRES<br>S              | NOTES |

| 0    | 1    | 1    | 1    | 0    | 14 x<br>DRAMsiz<br>e | (15 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 0    | 1    | 1    | 1    | 1    | 15 x<br>DRAMsiz<br>e | (16 x<br>DRAMsiz<br>e)-1 | 1,2   |

Table 1-2. DRAM Address as Viewed from the VMEbus (cont'd)

|      |      |      |      |      | BEGINN<br>ING        | ENDING                   |       |

|------|------|------|------|------|----------------------|--------------------------|-------|

| RBA4 | RBA3 | RBA2 | RBA1 | RBA0 | ADDRES<br>S          | ADDRES<br>S              | NOTES |

| 1    | 0    | 0    | 0    | 0    | 16 x<br>DRAMsiz<br>e | (17 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 1    | 0    | 0    | 0    | 1    | 17 x<br>DRAMsiz<br>e | (18 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 1    | 0    | 0    | 1    | 0    | 18 x<br>DRAMsiz<br>e | (19 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 1    | 0    | 0    | 1    | 1    | 19 x<br>DRAMsiz<br>e | (20 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 1    | 0    | 1    | 0    | 0    | 20 x<br>DRAMsiz<br>e | (21 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 1    | 0    | 1    | 0    | 1    | 21 x<br>DRAMsiz<br>e | (22 x<br>DRAMsiz<br>e)-1 | 1,2   |

| 1    | 0    | 1    | 1    | 0    | 22 x<br>DRAMsiz<br>e | (23 x<br>DRAMsiz<br>e)-1 | 1,2   |

**BEGINN ENDING ING ADDRES ADDRES** RBA4 RBA3 RBA2 RBA1 RBA0 NOTES S S 0 1 23 x (24 x 1,2 1 **DRAMsiz** DRAMsiz e)-1 1 1 0 0 0 24 x (25 x)1,2 DRAMsiz **DRAMsiz** e)-1 1 1 0 0 1 25 x (26 x)1,2 **DRAMsiz** DRAMsiz e)-1  $\mathbf{e}$ 1 1 0 1 0 26 x (27 x)1,2 DRAMsiz DRAMsiz e e)-1 1 1 0 1 1 27 x (28 x)1,2 **DRAMsiz** DRAMsiz e)-1 1 1 1 0 0 \$0000000 (1x)1,3,4 DRAMsiz e)-1 1 1 1 0 1 (2x)1,3,4 1 x **DRAMsiz** DRAMsiz e)-1

Table 1-2. DRAM Address as Viewed from the VMEbus (cont'd)

# NOT ES:

- DRAMsize = the size of the DRAM. For example, if the 4Mb version is used, then DRAMsize = \$400000, and (3 x DRAMsize)-1 = \$BFFFFF.

- 2. When beginning address is less then 16Mb, the DRAM responds to standard or extended address modifiers. When beginning address is 16Mb or greater, the DRAM responds to extended address modifiers only. Note that bits 4 and 5 in the VMEchip Slave Address Modifier Register further control response to standard and extended address modifiers.

- 3. This combination pertains only to DRAMsize of 16Mb or 32Mb.

- The values shown in the table refer to extended addresses only. In the standard address range the DRAM responds to \$000000 through \$7FFFFF.

Regardless of where the onboard RAM is located, the first 16Kb is used for 147Bug stack and static variable space and the rest is reserved as user space. Whenever the MVME147 is reset, the target PC is initialized to the address corresponding to the beginning of the user space and the target stack pointers are initialized to addresses within the user space.

The following abbreviated memory map for the MVME147 highlights addresses that might be of particular interest to you. Note that addresses are assumed to be hexadecimal throughout this manual. In text, numbers may be preceded with a dollar sign (\$) for identification as hexadecimal.

| DRAM LOCATIONS    | FUNCTION                                                                                              |

|-------------------|-------------------------------------------------------------------------------------------------------|

| 0000000-000003FF  | Target vector area                                                                                    |

| 00000400-000007FF | Bug vector area                                                                                       |

| 00000800-00000803 | MPCR (Multi-Processor Control Register)                                                               |

| 00000804-00000807 | MPAR (Multi-Processor Address Register)                                                               |

| 00000808-000037DF | Work area and stack for MVME147 debug                                                                 |

|                   | monitor                                                                                               |

| 000037E0-00003FFF | SCSI firmware work area                                                                               |

| EPROM LOCATIONS   | FUNCTION                                                                                              |

| FF800000-FF800003 | Supervisor stack address used when RESET switch is pressed.                                           |

| FF800004-FF800007 | Program Counter (PC) used when RESET switch is pressed.                                               |

| FF800008-FF80000B | Size of code                                                                                          |

| FF80000C-FF80000F | Reserved                                                                                              |

| FF83FFFA-FF83FFFB | Even/odd revision number of the two monitor EPROMs.                                                   |

| FF83FFFC-FF83FFFD | Even/odd socket number where monitor EPROMs reside.                                                   |

| FF83FFFE-FF83FFFF | Even/odd checksum of the two monitor EPROMs.                                                          |

|                   | \$FF800000 to \$FF83FFFF in sockets: U1 "U22" (even),                                                 |

|                   | U2 "U30" (odd)                                                                                        |

| FFA00000-FFBFFFFF | Reserved for user.                                                                                    |

|                   | $\protect\operatorname{SFFA00000}$ to $\protect\operatorname{SFFBFFFFF}$ in sockets: U16 "U1" (even), |

U18 "U15" (odd)

Note: "Uxx" denotes surface mount boards.

BBRAM LOCATIONS FUNCTION

FFFE0000-FFFE03FF Reserved for user

FFFE0000-FFFE000F Dynamic burnin pattern (0F-00 do burnin

loop in factory only)

FFFE0400-FFFE05FF Reserved for operating system use FFFE0600-FFFE06C1 Disk/Tape I/O Map, set via the **IOT**

command

FFFE06C2-FFFE073E Reserved for Bug use

FFFE073F Maintain Concurrent Mode through a Power

Cycle/Reset, set via the ENV command

(Y/N)

FFFE0741 VMEchip VMEbus Interrupt Handler Mask

Register

FFFE0742 Power up confidence test fail flag

FFFE0743 CPU clock frequency

FFFE0744-FFFE0745 Onboard console port number FFFE0746-FFFE0755 Serial port map (up to 8 ports)

FFFE0756 VMEchip Utility Interrupt Mask Register

FFFE0757 VMEchip Utility Interrupt Vector Register

FFFE0758 VMEchip GCSR Base Address Configuration

Register

FFFE0759 VMEchip Board Identification Register

FFFE075A-FFFE075B Checksum for VMEchip registers

FFFE075C-FFFE075F VBR saved for MEMFIND routine

FFFE0760-FFFE0761

Board base number (BCD)

FFFE0762

Board B number (BCD)

FFFE0763

Board Rev. letter (ASCII)

FFFE0764-FFFE0767 System offboard RAM start address

FFFE0768-FFFE076B System offboard RAM end address

FFFE076C Execute/Bypass SST memory test, set via

the ENV command

FFFE076D Board configuration register

FFFE076E Reset SCSI bus switch, set via RESET

command

| FFFE076F          | Reserved                                          |

|-------------------|---------------------------------------------------|

| FFFE0770          | Grafix board switch                               |

| FFFE0771          | Onboard diagnostic switch                         |

| FFFE0772          | System memory sizing flag                         |

| FFFE0773          | Execute/Bypass auto self test, set via ENV        |

|                   | command                                           |

| FFFE0774-FFFE0777 | End of onboard memory+1, set via memory           |

|                   | sizing routine                                    |

| FFFE0778-FFFE077A | Ethernet station address.                         |

| FFFE077B          | Onboard memory sizing flag.                       |

| FFFE077C-FFFE07A5 | SCSI firmware jump table                          |

| FFFE077C          | Jump to SCSI command entry                        |

| FFFE0782          | Jump to SCSI reactivation entry                   |

| FFFE0788          | Jump to SCSI interrupt entry                      |

| FFFE078E          | Jump to SCSI FUNNEL command entry                 |

| FFFE0794          | Jump to SCSI come-again entry                     |

| FFFE079A          | Jump to SCSI RTE entry                            |

| FFFE07A0-FFFE07A5 | Reserved                                          |

| FFFE07A6          | Local SCSI ID level (7)                           |

| FFFE07A7-FFFE07C5 | SCSI trace switches (reserved for internal        |

|                   | use).                                             |

| FFFE07C6          | AUTOboot controller number, set via ${f AB}$      |

|                   | command                                           |

| FFFE07C7          | AUTOboot device number, set via ${f AB}$          |

|                   | command                                           |

| FFFE07C8-FFFE07E3 | AUTOboot string, set via ${f AB}$ command         |

| FFFE07E4          | Off-board address multiplier, set via <b>OBA</b>  |

|                   | command                                           |

| FFFE07E5-FFFE07E9 | Reserved                                          |

| FFFE07EA-FFFE07EF | ROMboot direct address, set via ${f RB}$          |

|                   | command                                           |

| FFFE07F0          | AUTOboot enable switch, set via [NO]AB            |

|                   | command (Y/N)                                     |

| FFFE07F1          | AUTOboot at power up switch, set via              |

|                   | <b>AB</b> command (P/R)                           |

| FFFE07F2          | ROMboot enable switch, set via $[\mathbf{NO}]$ RB |

|                   |                                                   |

| command | (Y/N) |

|---------|-------|

|---------|-------|

FFFE07F3 ROMboot from VMEbus switch, set via **RB**

command (Y/N)

FFFE07F4 ROMboot at power up switch, set via **RB**

command (P/R)

FFFE07F5 RTC flag

FFFE07F6 Bug/System switch, set via ENV

command (B/S)

FFFE07F7 Reserved

FFFE07F8-FFFE07FF Time of day clock

#### I/O HARDWARE

| ADDRESSES         | FUNCTION                 |

|-------------------|--------------------------|

| FFFE3002-FFFE3003 | Serial port 1            |

| FFFE3000-FFFE3001 | Serial port 2            |

| FFFE3802-FFFE3803 | Serial port 3            |

| FFFE3800-FFFE3801 | Serial port 4            |

| FFFE2800          | Printer port             |

| FFFE1000-FFFE102F | PCC registers            |

| FFFE1800-FFFE1803 | LANCE (AM7990) registers |

| FFFE2000-FFFE201F | VME gate array registers |

| FFFE4000-FFFE401F | SCSI (WD33C93) registers |

## **Disk I/O Support**

147Bug can initiate disk input/output by communicating with intelligent disk controller modules over the VMEbus. Disk support facilities built into 147Bug consist of command-level disk operations, disk I/O system calls (only via the TRAP #15 instruction) for use by user programs, and defined data structures for disk parameters.

Parameters such as the address where the module is mapped and the type and number of devices attached to the controller module are kept in tables by 147Bug. Default values for these parameters are assigned at power up and cold-start reset, but may be altered as described in the *Default 147Bug Controller* and *Device Parameters* section in this chapter.

Appendix E contains a list of the controllers presently supported, as well as a list of the default configurations for each controller.

#### **Blocks Versus Sectors**

The logical block defines the unit of information for disk devices. A disk is viewed by 147Bug as a storage area divided into logical blocks. By default, the logical block size is set to 256 bytes for every block device in the system. The block size can be changed on a per device basis with the **IOT** command.

The sector defines the unit of information for the media itself, as viewed by the controller. The sector size varies for different controllers, and the value for a specific device can be displayed and changed with the **IOT** command.

When a disk transfer is requested, the start and size of the transfer is specified in blocks. The 147Bug translates this into an equivalent sector specification, which is then passed on to the controller to initiate the transfer. If the conversion from blocks to sectors yields a fractional sector count, an error is returned and no data is transferred.

## Disk I/O via 147Bug Commands

These following 147Bug commands are provided for disk I/O. Detailed instructions for their use are found in Chapter 3. When a command is issued to a particular controller LUN and device LUN, these LUNs are remembered by 147Bug so that the next disk command defaults to use the same controller and device.

### IOP (Physical I/O to Disk)

IOP allows you to read or write blocks of data, or to format the specified device in a certain way. **IOP** creates a command packet from the arguments specified by you, and then invokes the proper system call function to carry out the operation.

## IOT (I/O Teach)

**IOT** allows you to change any configurable parameters and attributes of the device. In addition, it allows you to see the controllers available in the system.

## IOC (I/O Control)

**IOC** allows you to send command packets as defined by the particular controller directly. **IOC** can also be used to look at the resultant device packet after using the **IOP** command.

#### **BO (Bootstrap Operating System)**

**BO** reads an operating system or control program from the specified device into memory, and then transfers control to it.

#### **BH** (Bootstrap and Halt)

**BH** reads an operating system or control program from a specified device into memory, and then returns control to 147Bug. It is used as a debugging tool.

## Disk I/O via 147Bug System Calls

All operations that actually access the disk are done directly or indirectly by 147Bug TRAP #15 system calls. (The command-level disk operations provide a convenient way of using these calls without writing and executing a program.)

The following system calls are provided to allow user programs to do disk I/O:

.DSKRD - Disk read. System call to read blocks from disk/tape into

memory.

**.DSKWR** - Disk write. System call to write blocks from memory onto

disk/tape.

**.DSKCFIG** - Disk configure. This function allows you to change the

configuration of the specified device.

**.DSKFMT** - Disk format. This function allows you to send a format

command to the specified device.

**.DSKCTRL** - Disk control. This function is used to implement any special

device control functions that cannot be accommodated easily

with any of the other disk/tape functions.

Refer to Chapter 5 for information on using these and other system calls.

To perform a disk operation, 147Bug must eventually present a particular disk controller module with a controller command packet which has been especially prepared for that type of controller module. (This is accomplished in the respective controller driver module.) A command packet for one type of controller module usually does not have the same format as a command packet for a different type of module. The system call facilities which do disk I/O accept a generalized (controller-independent) packet format as an

argument, and translate it into a controller-specific packet, which is then sent to the specified device. Refer to the system call descriptions in Chapter 5 for details on the format and construction of these standardized user packets.

The packets which a controller module expects to be given vary from controller to controller. The disk driver module for the particular hardware module (board) must take the standardized packet given to a trap function and create a new packet which is specifically tailored for the disk drive controller it is sent to. Refer to documentation on the particular controller module for the format of its packets, and for using the IOC command.

## **Default 147Bug Controller and Device Parameters**

The **IOT** command, with the **T** (teach) option specified, must be invoked to initialize the parameter tables for available controllers and devices. This option instructs **IOT** to scan the system for all currently supported disk/tape controllers (refer to Appendix E) and build a map of the available controllers. This map is built in the Bug RAM area, but can also be saved in NVRAM if so instructed. If the map is saved in NVRAM, then after a reset, the map residing in NVRAM is copied to the Bug RAM area and used as the working map. If the map is not saved in NVRAM, then the map is temporary and the **IOT;T** command must be invoked again if a reset occurs.

If the device is formated and has a configuration area, then during the first device access or during a boot, **IOT** is not required. Reconfiguration is done automatically by reading the configuration area from the device, then the discriptor for the device is modified according to the parameter information contained in the configuration area. (Appendix D has more information on the disk configuration area.)

If the device is not formated or of unknown format, or has no configuration area, then before attempting to access the device, you should verify the parameters, using **IOT**. The **IOT** command may be used to manually reconfigure the parameter table for any controller and/or device that is different from the default. These are temporary changes and are overwritten with default parameters, if a reset occurs.

The **IOT;T** command should also be invoked any time the controllers are changed or when ever the NVRAM map has been damaged or not initialized ("No Disk Controllers Available").

### **Disk I/O Error Codes**

The 147Bug returns an error code if an attempted disk operation is unsuccessful. Refer to Appendix F for an explanation of disk I/O error codes.

## **Multiprocessor Support**

The MVME147 dual-port RAM feature makes the shared RAM available to remote processors as well as to the local processor.

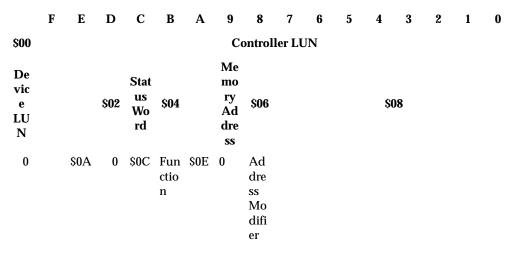

A remote processor can initiate program execution in the local MVME147 dual- port RAM by issuing a remote **GO** command using the Multiprocessor Control Register (MPCR). The MPCR, located at shared RAM location base address plus \$800, contains one of two longwords used to control communication between processors. The MPCR contents are organized as follows:

| Base Address | * | N/A | N/A | N/A | MPCR |

|--------------|---|-----|-----|-----|------|

| + \$800      |   |     |     |     |      |

The status codes stored in the MPCR are of two types:

Status returned (from the monitor)

Status set by the bus master (job requested by some processor)

The status codes that may be returned from the monitor are:

| HEX 0   | (HEX 00) | _ | Wait. Initialization not yet complete. |

|---------|----------|---|----------------------------------------|

| ASCII R | (HEX 52) | _ | Ready. The firmware is watching for    |

|         |          |   | a change.                              |

| ASCII E | (HEX 45) | _ | Code pointed to by the MPAR is         |

|         |          |   | executing.                             |

The status code that may be set by the bus master is:

ASCII G (HEX 47) — Use Go Direct (**GD**) logic specifying the MPAR address.

ASCII B (HEX 42) — Recognize breakpoints using the Go

(G) logic.

The Multiprocessor Address Register (MPAR), located in shared RAM location base address plus \$804, contains the second of two longwords used to control communication between processors. The MPAR contents specify the address at which execution for the remote processor is to begin if the MPCR contains a G or a B. The MPAR is organized as follows:

Base Address MSB \* \* LSB MPAR + \$804

At power up, the debug monitor self-test routines initialize RAM, including the memory locations used for multiprocessor support (\$800 through \$807).

The MPCR contains \$00 at power up, indicating that initialization is not yet complete. As the initialization proceeds, the execution path comes to the "prompt" routine. Before sending the prompt, this routine places an R in the MPCR to indicate that initialization is complete. Then the prompt is sent.

If no terminal is connected to the port, the MPCR is still polled to see whether an external processor requires control to be passed to the dual-port RAM. If a terminal does respond, the MPCR is polled for the same purpose while the serial port is being polled for your input.

An ASCII G placed in the MPCR by a remote processor indicates that the Go Direct type of transfer is requested. An ASCII B in the MPCR indicates that previously set breakpoints are enabled when control is transferred (as with the Go command).

In either sequence, an E is placed in the MPCR to indicate that execution is underway just before control is passed to the execution address. (Any remote processor could examine the MPCR contents.)

If the code being executed is to reenter the debug monitor, a TRAP #15 call using function \$0063 (SYSCALL .RETURN) returns control to the monitor with a new display prompt. Note that every time the debug monitor returns to the prompt, an R is moved into the MPCR to indicate that control can be transferred once again to a specified RAM location.

# **Diagnostic Facilities**

Included in the 147Bug package is a complete set of hardware diagnostics intended for testing and troubleshooting of the MVME147 (refer to Chapter 6). In order to use the diagnostics, you must switch directories to the diagnostic directory. If in the debugger directory, you can switch to the diagnostic directory by entering the debugger command Switch Directories (SD). The diagnostic prompt ("147-Diag>") should appear. Refer to Chapter 6 for complete descriptions of the diagnostic routines available and instructions on how to invoke them. Note that some diagnostics depend on restart defaults that are set up only in a particular restart mode. Refer to the documentation on a particular diagnostic for the correct mode.

## **Related Documents**

The following publications are applicable to the MVME147BUG debugging package and may provide additional helpful information. If not shipped with this product, they may be purchased by contacting your local Motorola sales office. Non-Motorola documents may be obtained from the sources listed.

|                                                | MOTOROLA              |

|------------------------------------------------|-----------------------|

| DOCUMENT TITLE                                 | PUBLICATION<br>NUMBER |

| MVME050 System Controller<br>Module User's     | MVME050               |

| Manual                                         |                       |

| MVME701A I/O Transition<br>Module User's       | MVME701A              |

| Manual                                         |                       |

| MVME147 MPU VMEmodule<br>User's Manual         | MVME147               |

| or                                             |                       |

| MVME147S MPU VMEmodule<br>User's Manual        | MVME147S              |

| MC68030 32-Bit<br>Microprocessor User's Manual | MC68030UM             |

| MC68881/MC68882 Floating-<br>Point Coprocessor | MC68881UM             |

| User's Manual                                  |                       |

|                             | MOTOROLA              |

|-----------------------------|-----------------------|

| DOCUMENT TITLE              | PUBLICATION<br>NUMBER |

| MVME147FW SCSI Firmware     | MVME147FW             |

| User's Manual               |                       |

| MVME319 Intelligent         | MVME319               |

| Disk/Tape Controller User's |                       |

| Manual                      |                       |

| MVME320A VMEbus Disk        | MVME320A              |

| Controller Module           |                       |

| User's Manual               |                       |

| MVME320B VMEbus Disk        | MVME320B              |

| Controller Module           |                       |

| User's Manual               |                       |

| MVME321 Intelligent Disk    | MVME321               |

| Controller User's           |                       |

| Manual                      |                       |

| MVME321 IPC Firmware        | MVME321FW             |

| User's Guide                |                       |

| MVME327A VMEbus to SCSI     | MVME327A              |

| Bus Adapter                 |                       |

| and MVME717 Transition      |                       |

| Module                      |                       |

| User's Manual               |                       |

|                                                | MOTOROLA              |

|------------------------------------------------|-----------------------|

| DOCUMENT TITLE                                 | PUBLICATION<br>NUMBER |

| MVME350 Streaming Tape<br>Controller VMEmodule | MVME350               |

| User's Manual                                  |                       |

| MVME350 IPC Firmware<br>User's Manual          | MVME350FW             |

| MVME360 SMD Disk<br>Controller User's Manual   | MVME360               |

|                                             | MOTOROLA              |

|---------------------------------------------|-----------------------|

| DOCUMENT TITLE                              | PUBLICATION<br>NUMBER |

| VERSAdos to VME Hardware and Software       | MVMEVDOS              |

| Configuration User's<br>Manual              |                       |

| M68000 Family VERSAdos<br>System Facilities | M68KVSF               |

| Reference Manual                            |                       |

#### NOTE:

Although not shown in the above list, each Motorola MCD manual publication number is suffixed with characters which represent the revision level of the document; i.e., /D2 (the second revision of a manual); supplement bears the same number as the manual but has a suffix; i.e, /A1 (the first supplement to the manual).

The following publications are available from the sources indicated.

Z8530A Serial Communications Controller data sheet; Zilog, Inc., Corporate Communications, Building A, 1315 Dell Ave, Campbell, California 95008

SCSI Small Computer System Interface; draft X3T9.2/82-2 - Revision 14; Computer and Business Equipment Manufacturers Association, 311 First Street, N. W., Suite 500, Washington D.C. 20001

MK48T02 2K x 8 ZEROPOWER/TIMEKEEPER RAM data sheet; Thompson Components- Mostek Corporation, 1310 Electronics Drive, Carrollton, Texas 75006

WD33C93 SCSI-Bus Interface Controller; WESTERN DIGITAL Corporation, 2445 McCabe Way, Irvine, California 92714

Local Area Network Controller Am7990 (LANCE), Technical Manual, order number 06363A, Advanced Micro Devices, Inc., 901 Thompson Place, P.O Box 3453, Sunnyvale, CA 94088.

# **Manual Terminology**

Throughout this manual, a convention has been maintained whereby data and address parameters are preceded by a character which specifies the numeric format as follows:

| \$ | dollar    | specifies a hexadecimal<br>number |

|----|-----------|-----------------------------------|

| %  | percent   | specifies a binary number         |

| &  | ampersand | specifies a decimal number        |

Unless otherwise specified, all address references are in hexadecimal An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

# **Entering Debugger Command Lines**

The 147Bug is command-driven and performs its various operations in response to the commands entered at the keyboard. When the debugger prompt 147-Bug> appears on the terminal screen then the debugger is ready to accept commands.

As the command line is entered it is stored in an internal buffer. Execution begins only after the carriage return is entered, thus allowing you to correct entry errors, if necessary.

When a command is entered the debugger executes the command and the prompt reappears. However, if the command entered causes execution of your target code; i.e., **GO**, then control may or may not return to the debugger, depending on what the your program does. For example, if a breakpoint has been specified, then control is returned to the debugger when the breakpoint is encountered during execution of your program. Alternately, your program could return control to the debugger by means of the TRAP #15 function .RETURN (described in Chapter 5). For more about this, refer to the description in Chapter 3 for the **GO** commands.

In general, a debugger command is made up of the following parts:

- 1. The command identifier; i.e., **MD** or **md** for the memory display command. Note that either upper- or lower-case may be used.

- $2. \quad A \ port \ number, \ if \ the \ command \ is \ set \ up \ to \ work \ with \ more \ than \ one \ port.$

- 3. At least one intervening space before the first argument.

- 4. Any required arguments, as specified by the command.

- 5. An option field, set off by a semicolon (;) to specify conditions other than the default conditions of the command.

When entering a command at the prompt the following control codes may be entered for limited command line editing, if necessary, using the control characters described below.

Note

The presence of the upward caret, ^, before a character indicates that the Control or CTRL key must be held down

## while striking the character key.

| ^ <b>X</b> | (cancel line)       | _ | The cursor is backspaced to the beginning of the line. If the terminal port is configured with the hardcopy or TTY option (see <b>PF</b> command) then a carriage return and line feed is issued along with another prompt. |

|------------|---------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ^ <b>H</b> | (backspace)         | _ | The cursor is moved back one position. The character at the new cursor position is erased. If the hardcopy option is selected a "/" character is typed along with the deleted character.                                    |

| del        | (delete/rubo<br>ut) | _ | Performs the same function as ${}^{\wedge}H$ .                                                                                                                                                                              |

| <b>^D</b>  | (redisplay)         | _ | The entire command line as entered so far is redisplayed on the following line.                                                                                                                                             |

When observing output from any 147Bug command, the XON and XOFF characters which are in effect for the terminal port may be entered to control the output, if the XON/XOFF protocol is enabled (default). These characters are initialized to  ${}^{\circ}\mathbf{S}$  and  ${}^{\circ}\mathbf{Q}$  respectively by 147Bug but may be changed by using the **PF** command. In the initialized (default) mode, operation is as follows:

| ^ <b>S</b> | (wait)   | _ | Console output is halted.  |

|------------|----------|---|----------------------------|

| ^ <b>Q</b> | (resume) | _ | Console output is resumed. |

The following conventions are used in the command syntax, examples, and text in this manual:

| boldface strings | A boldface string is a literal such as a command or a program name, and is to be typed just as it appears. |

|------------------|------------------------------------------------------------------------------------------------------------|

| italic strings   | An italic string is a "syntactic variable" and is to be replaced by one of a class of items it represents. |

| Fixed font       | Used throughout in examples of screen data.                                                                |

| 1  | A vertical bar separating two or more items indicates that a choice is to be made; only one of the items separated by this symbol should be selected. |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| [] | Square brackets enclose an item that is optional. The item may appear zero or one time.                                                               |

| [] | Square brackets, followed by an ellipsis (three dots) enclose an item that is optional/repetitive. The item may appear zero or more times.            |

Operator inputs are to be followed by a carriage return. The carriage is shown as (**CR**), only if it is the only input required.

## **Syntactic Variables**

The following syntactic variables are encountered in the command descriptions which follow. In addition, other syntactic variables may be used and are defined in the particular command description in which they occur.

| del   | _ | Delimiter; either a comma or a space.                                                                         |

|-------|---|---------------------------------------------------------------------------------------------------------------|

| exp   | _ | Expression (described in detail in the <i>Expression as a Parameter</i> section in this chapter).             |

| addr  | _ | Address (described in detail in the <i>Address as a Parameter</i> section in this chapter).                   |

| count | _ | Count; the syntax is the same as for <exp>.</exp>                                                             |

| range | _ | A range of memory addresses which may be specified either by <i>addr del addr</i> or by <i>addr : count</i> . |

| text  | _ | An ASCII string of up to 255 characters, delimited at each end by the single quote mark (').                  |

### **Expression as a Parameter**

An expression can be one or more numeric values separated by the arithmetic operators: plus (+), minus (-), multiplied by (\*), divided by (/), logical AND (&), shift left (<<), or shift right (>>).

Numeric values may be expressed in either hexadecimal, decimal, octal, or binary by immediately preceding them with the proper base identifier. The following table lists numeric value examples.

| BASE        | IDENTIFIER | EXAMPLES      |  |  |

|-------------|------------|---------------|--|--|

| Hexadecimal | \$         | \$FFFFFFF     |  |  |

| Decimal     | &          | &1974, &10-&4 |  |  |

| Octal       | @          | @456          |  |  |

| Binary      | %          | %1000110      |  |  |

If no base identifier is specified, then the numeric value is assumed to be hexadecimal.

A numeric value may also be expressed as a string literal of up to four characters. The string literal must begin and end with the single quote mark ('). The numeric value is interpreted as the concatenation of the ASCII values of the characters. This value is right-justified, as any other numeric value would be. The following table lists string literal examples.

| STRING LITERAL | NUMERIC VALUE (in Hex) |  |

|----------------|------------------------|--|

| 'A'            | 41                     |  |

| 'ABC'          | 414243                 |  |

| 'TEST'         | 54455354               |  |

Evaluation of an expression is always from left to right unless parentheses are used to group part of the expression. There is no operator precedence. Sub-expressions within parentheses are evaluated first. Nested parenthetical sub-expressions are evaluated from the inside out. The following table lists examples of valid expressions.

| EXPRESSION      | RESULT (in Hex) | NOTES       |

|-----------------|-----------------|-------------|

| FF0011          | FF0011          |             |

| 45+99           | DE              |             |

| &45+&99         | 90              |             |

| @35+@67+@10     | 5C              |             |

| %10011110+%1001 | A7              |             |

| 88<<4           | 880             | shift left  |

| AA&F0           | A0              | logical AND |

The total value of the expression must be between 0 and \$FFFFFFF.

#### Address as a Parameter

Many commands use addr as a parameter. The syntax accepted by 147Bug is similar to the one accepted by the MC68030 one-line assembler. All control addressing modes are allowed. An "~address+ offset register"~ mode is also provided.

#### **Address Formats**

Table 2-1 summarizes the address formats which are acceptable for address parameters in debugger command lines.

**Table 2-3. Debugger Address Parameter Formats**

| FORMAT                                                  | EXAMPLE                     | DESCRIPTION                                                                                    |  |  |  |

|---------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------|--|--|--|

| N                                                       | 140                         | Absolute address+contents of automatic offset register.                                        |  |  |  |

| N+Rn                                                    | 130+R5                      | Absolute address+contents of the specified offset register (not an assembler-accepted syntax). |  |  |  |

| (An)                                                    | (A1)                        | Address register indirect.                                                                     |  |  |  |

| (d,An) or<br>d(An)                                      | (120,A1)<br>120(A1)         | Address register indirect with displacement (two formats accepted).                            |  |  |  |

| (d,An,Xn) or<br>d(An,Xn)                                | (&120,A1,D2)<br>&120(A1,D2) | Address register indirect with index and displacement (two formats accepted).                  |  |  |  |

| ([bd,An,Xn],od)                                         | ([C,A2,A3],&100)            | Memory indirect preindexed.                                                                    |  |  |  |

| ([bd,An],Xn,od)                                         | ([12,A3],D2,&10)            | Memory indirect postindexed.                                                                   |  |  |  |

| For the memory indirect modes, fields can be omitted.   |                             |                                                                                                |  |  |  |

| For example, three of many permutations are as follows: |                             |                                                                                                |  |  |  |

| ([,An],od)                                              | ([,A1],4)                   |                                                                                                |  |  |  |

| ([bd])                                                  | ([FC1E])                    |                                                                                                |  |  |  |

| ([bd,,Xn])                                              | ([8,,D2])                   |                                                                                                |  |  |  |

| Notes: | N  | _ | Absolute address(any valid expression). |

|--------|----|---|-----------------------------------------|

|        | An | _ | Address register n.                     |

| Xn | _ | Index register n (An or Dn).               |

|----|---|--------------------------------------------|

| d  | _ | Displacement (any valid expression).       |

| bd | _ | Base displacement (any valid expression).  |

| od | _ | Outer displacement (any valid expression). |

| n  | _ | Register number (0 to 7).                  |

| Rn | _ | Offset register n.                         |

## **Offset Registers**

Eight pseudo-registers (R0 through R7) called offset registers are used to simplify the debugging of relocatable and position-independent modules. The listing files in these types of programs usually start at an address (normally 0) that is not the one in which they are loaded, so it is harder to correlate addresses in the listing with addresses in the loaded program. The offset registers solve this problem by taking into account this difference and forcing the display of addresses in a relative address+offset format. Offset registers have adjustable ranges and may even have overlapping ranges. The range for each offset register is set by two addresses: base and top. Specifying the base and top addresses for an offset register sets its range. In the event that an address falls in two or more offset registers' ranges, the one that yields the least offset is chosen. For additional information about the offset registers, see the **OF** command description.

Relative addresses are limited to 1Mb (5 digits), regardless of the range of the closest offset register.

Example: A p

A portion of the listing file of a relocatable module assembled with the MC68030 VERSAdos Resident Assembler is shown below:

```

1

2

3

MOVE STRING SUBROUTINE

4

5

0 00000000 48E78080

MOVESTR MOVEM.L D0/A0,-(A7)

6

0 00000004 4280

CLR.L

D0

7

0 00000006 1018

MOVE.B

(A0) + , D0

0 00000008 5340

SUBQ.W

#1,D0

LOOP

0 0000000A 12D8

MOVE.B

(A0) + , (A1) +

0 0000000C 51C8FFFC

10

MOVS

DBRA

D0,LOOP

0 00000010 4CDF0101

11

MOVEM.L (A7)+,D0/A0

12

0 00000014 4E75

RTS

13

END

14

TOTAL ERRORS

TOTAL WARNINGS

```

The above program was loaded at address \$0001327C.

The disassembled code is shown next:

```

147Bug>MD 1327C;DI

0001327C 48E78080

MOVEM.L D0/A0,-(A7)

00013280 4280

CLR.L

D0

00013282 1018

MOVE.B

(A0) + , D0

00013284 5340

#1,D0

SUBQ.W

00013286 12D8

MOVE.B

(A0) + , (A1) +

00013288 51C8FFFC

D0,$13286

DBF

0001328C 4CDF0101

(A7) + , D0/A0

MOVEM.L

00013290 4E75

RTS

147Bug>

```

By using one of the offset registers, the disassembled code addresses can be made to match the listing file addresses as follows:

```

147Bug>OF R0

R0 =00000000 00000000? 1327C:16. < CR >

147Bug>MD 0+R0;DI <CR>

00000+R0 48E78080

MOVEM.L D0/A0,-(A7)

00004+R0 4280

CLR.L

D0

00006+R0 1018

MOVE.B (A0)+,D0

SUBO.W #1,D0

00008+R0 5340

0000A+R0 12D8

MOVE.B (A0) + , (A1) +

0000C+R0 51C8FFFC

DBF

D0,$A+R0

00010+R0 4CDF0101

MOVEM.L (A7)+,D0/A0

00014+R0 4E75

RTS

147Bug>

```

#### **Port Numbers**

Some 147Bug commands give you the option of choosing the port which is to be used to input or output. The valid port numbers which may be used for these commands are:

| 0 | - MVME147 RS-232C<br>(MVME712/MVME712M<br>serial port 1) | M |

|---|----------------------------------------------------------|---|

| 1 | - MVME147 RS-232C<br>(MVME712/MVME712M<br>serial port 2) | M |

| 2 | - MVME147 RS-232C<br>(MVME712/MVME712M<br>serial port 3) | M |

| 3 | - MVME147 RS-232C<br>(MVME712/MVME712M<br>serial port 4) | M |

| 4 | - MVME147 Printer Port<br>(MVME712/MVME712M<br>printer)  | M |

Note

These logical port numbers (0, 1, 2, 3, and 4) are referred to as "Serial Port 1", "Serial Port 2", "Serial Port 3", "Serial Port 4", and "Printer Port", respectively, by the MVME147

hardware documentation and by the MVME712/MVME712M hardware documentation.

For example, the command DU1 (Dump S-records to Port 1) would actually output data to the device connected to the serial port labeled SERIAL PORT 2 on the MVME712/MVME712M panel.

# **Entering and Debugging Programs**

There are various ways to enter your program into system memory for execution. One way is to create the program using the Memory Modify (MM) command with the assembler/disassembler option. The program is entered one source line at a time. After each source line is entered, it is assembled and the object code is loaded to memory. Refer to Chapter 4 for complete details of the 147Bug assembler/disassembler.

Another way to enter a program is to download an object file from a host system. The program must be in S-record format (described in Appendix C) and may have been assembled or compiled on the host system. Alternately, the program may have been previously created using the 147Bug MM command as outlined above and stored to the host using the DU command. If a communication link exists between the host system and the MVME147 then the file can be downloaded from the host into MVME147 memory via the debugger LO command.

One more way is by reading in the program from disk, using one of the disk commands; i.e., **BO**, **BH**, or **IOP**. When the object code has been loaded into memory, you can set breakpoints if desired and run the code or trace through it.

# System Utility Calls from Your Programs

A convenient way of doing character input/output, and many other useful operations has been provided so that you do not have to write these routines into the target code. You have access to various 147Bug routines via the MC68030 TRAP #15 instruction. Refer to Chapter 5 for details on the various TRAP #15 utilities available and how to invoke them from within your program.

# **Preserving Debugger Operating Environment**

This section explains how to avoid contaminating the operating environment of the debugger. 147Bug uses certain of the MVME147 onboard resources and uses onboard memory to contain temporary variables, exception vectors, etc. If you disturb resources which 147Bug depends on, then the debugger may function unreliably or not at all.

## 147Bug Vector Table and Workspace

As described in the *Memory Requirements* section in Chapter 1, 147Bug needs 16Kb of read/write memory to operate. The 147Bug reserves a 1024-byte area for a user program vector table area and then allocates another 1024-byte area and builds an exception vector table for the debugger itself to use. Next, 147Bug reserves space for static variables and initializes these static variables to predefined default values. After the static variables, 147Bug allocates space for the system stack, then initializes the system stack pointer to the top of this area.